# OPERATIONAL MANUAL

FOR

# Minispace

THE SOLARTRON ELECTRONIC GROUP LTD

Thames Ditton, Surrey, England

# THE MINISPACE ANALOGUE COMPUTER OPERATING MANUAL

#### FOREWORD

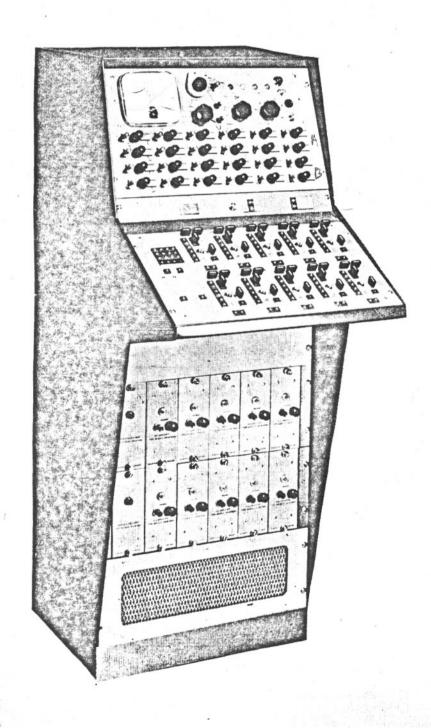

The Minispace analogue computer is a small general purpose machine suitable as a design tool or as an educational aid. It comprises ten drift-corrected D.C. amplifiers, each of which may be used for summing, sign reversing, or integrating, twenty-four potentiometers, a patching panel, computer control facilities and built-in power supplies. Simple non-linear elements are included, and servo-multipliers are readily incorporated to expand the scope of the computer. Two Minispace machines may be used in conjunction with one another, with one control unit operating both machines.

The following problems are typical of those which may be solved on a single Minispace.

- (a) Single differential equations of up to fifth order.

- (b) Two simultaneous differential equations, up to third order.

- (c) Multiple loop servo-systems.

- (d) Aerodynamics simulation for guided weapon control systems.

- (e) Dynamical mechanical systems, of for instance, the mass, spring, viscous damping type.

## THE SOLARTRON ELECTRONIC GROUP LTD

THAMES DITTON · SURREY · ENGLAND

Telephone: EMBerbrook 5522

Telegrams and Cables: Solartron, Thames Ditton

### LIST OF CONTENTS

## Chapter 1. Basic Analogue Computing Techniques

| 1.1              | Introduction                | • • • •     | • • • •   | • • • •    |                                         | • • • • | • • • • | • • • • | 5  |  |  |

|------------------|-----------------------------|-------------|-----------|------------|-----------------------------------------|---------|---------|---------|----|--|--|

| 1.2              | Basic Mathematical Opera    | tions       | ••••      |            | ••••                                    |         | ••••    |         | 5  |  |  |

| 1.3              | Setting up a Problem and I  | Programi    | ming the  | Computer   | r                                       | ••••    |         |         | 8  |  |  |

| 1.4              | Simulating simple disconti  | nuities     |           |            |                                         |         |         |         | 12 |  |  |

|                  | Ch                          | apter 2.    | Operation | ng Minisp  | ace                                     |         | •       |         |    |  |  |

| 2.1.             | General description of Mir  | nispace     | ••••      |            |                                         |         |         |         | 14 |  |  |

| 2.2              | Setting up Procedure        |             |           |            |                                         | ••••    | • • • • |         | 15 |  |  |

| 2.3              | Patching Minispace          |             |           |            |                                         | • • • • | • • • • |         | 16 |  |  |

| 2.4              | Computer Functions          |             | • • • •   |            | • • • •                                 | • • • • |         |         | 20 |  |  |

|                  |                             |             | Appendic  | es         |                                         |         |         |         |    |  |  |

| Append           | dix 1                       |             |           |            |                                         |         |         |         |    |  |  |

| прреп            | Specification of DC Ampli   | fier AA62   | 21.2      |            | ••••                                    | • • • • |         | • • • • | 23 |  |  |

| Append           | dix 2                       |             |           |            | (X. 1)                                  |         |         |         |    |  |  |

|                  | The differentiating Circuit | t           | • • • •   | ••••       | • • • •                                 |         |         | • • • • | 23 |  |  |

| Append           |                             |             |           |            |                                         |         |         |         |    |  |  |

|                  | Computer limitations        | • • • •     |           | • • • •    | • • • •                                 |         | • • • • | • • • • | 24 |  |  |

| LIST OF DIAGRAMS |                             |             |           |            |                                         |         |         |         |    |  |  |

| 19 1             | The DC Amplifier with gen   | neralised   | forward   | path and   | feedback                                | impedar | nces    |         | 5  |  |  |

| 2                | An Integrator               | • • • •     | ••••      | ••••       |                                         | • • • • | ••••    | • • • • | 7  |  |  |

| Fig. 3           | Circuit for simple lag      | • • • •     | ••••      | ••••       |                                         |         | • • • • |         | 7  |  |  |

| Fig. 4           | Coefficient Potentiometer   | • • • •     | ••••      | ••••       | ••••                                    | ••••    | • • • • | • • • • | 8  |  |  |

| Fig. 5           | Coefficient Potentiometer   | in the fe   | edback P  | ath        | ••••                                    |         | ••••    | • • • • | 8  |  |  |

| Fig. 6           | Computer flow diagram for   | r second    | order di  | ifferentia | l equation                              | 1       | • • • • |         | 9  |  |  |

| Fig. 7           | Computer schematic diag     | • • • •     | • • • •   | 9          |                                         |         |         |         |    |  |  |

| Fig. 8           | Scaled computer diagram     | for $y = k$ | x         | ••••       | ••••                                    | • • • • | ••••    | • • • • | 11 |  |  |

| Fig. 9           | Circuit for inert zone      | • • • •     | • • • •   |            | • • • •                                 | ••••    |         | • • • • | 12 |  |  |

| Fig. 10          | Limiter circuit             |             | ••••      |            | ••••                                    | ••••    | • • • • |         | 12 |  |  |

| Fig. 1           | 1 Two segment curve         |             |           |            | • • • • • • • • • • • • • • • • • • • • | ••••    |         |         | 12 |  |  |

| Fig. 1           | 2 Backlash simulation       |             |           |            | ••••                                    | ••••    |         |         | 13 |  |  |

## LIST OF DIAGRAMS (continued)

| VICES ACCOUNT      |                      |           |            |           |      |         |         |      |                         |

|--------------------|----------------------|-----------|------------|-----------|------|---------|---------|------|-------------------------|

| ig. 13 Samming     | circuit              | • • • •   | • • • •    | ••••      |      | • • • • |         |      | 18                      |

| Fig. 14 Simple la  | g                    | • • • •   |            | • • • •   |      | • • • • |         |      | 18                      |

| Fig. 15 Multiplyin | ng and dividing by   | y a cons  | tant       |           |      |         |         |      | 19                      |

| ig. 16 Circuit fo  | or setting coeffici  | ent Pote  | entiomete  | r         |      | • • • • | • • • • |      | 21                      |

| Fig. 17 Setting in | itial conditions     | •• 5.     |            |           |      | ••••    |         |      | 21                      |

| Fig. 18 The diffe  | rentiating circuit   |           | ••••       | ••••      |      |         |         |      | 23                      |

| ig. 19 Generalis   | sed computer am      | olifier i | n open loo | p conditi | ons  | • • • • |         |      | 24                      |

| Fig. 20 Minispac   | e Patch Panel        | ••••      |            |           | •••• | ••••    |         | •••• | inside<br>rear<br>cover |

| Fig. 21 Coefficie  | nt setting potention | ometers   | ••••       |           |      | ••••    | ••••    | •••• | inside<br>rear<br>cover |

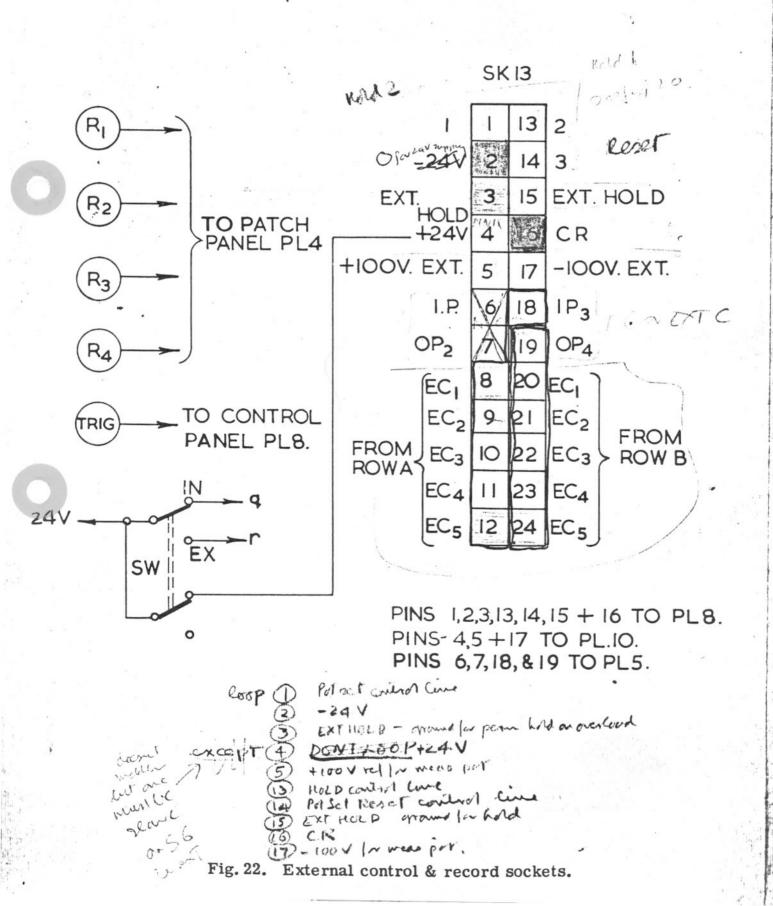

| Fig. 22 External   | control & record     | sockets   | 3          |           | •••• | ••••    | ••••    | •••• | inside<br>rear<br>cover |

|                    |                      | LIST (    | OF PHOTO   | OGRAPHS   | 5    |         |         |      |                         |

| rontispiece        | Minispace            | Si .      |            | • • • •   |      |         |         |      | 4                       |

| Plate 1            | Control and pot      | entiome   | ter Panel  |           |      |         |         |      | 14                      |

| 21-4- 0            | m, p, , , p          |           |            |           |      |         |         |      |                         |

Frontispiece Minispace

#### CHAPTER 1

#### BASIC ANALOGUE COMPUTING TECHNIQUES

#### 1.1 Introduction

The equations which describe many real physical systems are not amenable to classical methods of analysis due to inherent non-linearities. Others may be difficult and tedious to solve because of general complexity, or because solutions of the same equation are required with many values of the physical constant. This is particularly so, for example, in problems of system optimisation, where insufficient initial information exists to enable those constants to be chosen directly. In such cases it is desirable to set up a model (an analogue) of the system to be studied, provided this can be done with reasonable facility. This is precisely the function of the analogue computer.

The electronic analogue computer is in fact, a model in which the physical variables are represented as voltage variations, mathematical operations on these variables being performed using direct coupled, high gain feedback amplifiers, whilst the coefficients (physical constants) multiplying the variables are set up on continuously variable attenuators (potentiometers).

Generally, the most suitable applications for electronic analogue computers are those in which the independent variable is time, both transient and steady state solutions being readily obtainable from the analogue.

#### 1.2 Basic Mathematical Operations

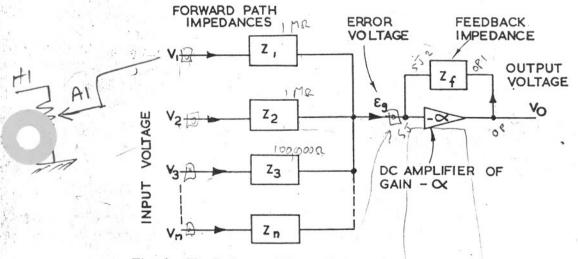

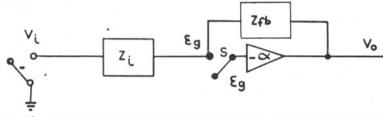

## (1) The D.C. amplifier with generalised forward path and feedback impedances.

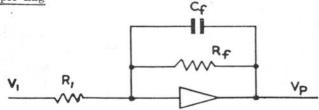

Fig. 1. The D.C. amplifier with generalised forward path and feedback impedances.

The amplifier input impedance is high so the current into the amplifier is assumed zero.

Summing currents at the input node

$$\frac{\mathbf{V_1} - \mathbf{E_g}}{\mathbf{Z_1}} + \frac{\mathbf{V_2} - \mathbf{E_g}}{\mathbf{Z_2}} + \dots \qquad \frac{\mathbf{V_n} - \mathbf{E_g}}{\mathbf{Z_n}} + \frac{\mathbf{V_o} - \mathbf{E_g}}{\mathbf{Z_f}} = 0$$

$$V_0 = -\infty E_g$$

Then

$$\frac{V_1 + \underline{V_0}}{Z_1} + \frac{V_2 + \underline{V_0}}{Z_2} + \dots + \frac{V_n + \underline{V_0}}{Z_n} + \frac{V_0 + \underline{V_0}}{Z_f} = 0$$

or re-writing

$$\frac{V_1+V_2+\ldots V_n}{\overline{Z_1}}=-V_0\left(\frac{1}{\overline{Z_1}}+\frac{1}{\sqrt{Z_1}}+\frac{1}{\sqrt{Z_2}}+\frac{1}{\sqrt{Z_n}}+\frac{1}{\sqrt{Z_f}}\right)$$

If  $\propto$  is very large, the terms multiplied by  $\frac{1}{\propto}$  within the  $V_0$  bracket may be neglected, and then.

$$V_0 = -\left(V_1 \frac{Z_f + V_2}{Z_1} \frac{Z_f}{Z_2} + \dots \frac{V_n Z_f}{Z_n}\right)$$

Depending on the value of the number of inputs is limited, since the effective amplifier loop gain and the accuracy of the computation is decreased as the value of the forward path impedances paralleled is decreased.

Note:  $V_0$ ,  $V_1$ ,  $V_2$ , etc. are of similar orders of magnitude; from equation II above, since  $\infty$  is very large  $E_g$  is always vanishingly small. Thus the summing node is termed a virtual earth.

#### (2) Sign Reversal

Referring to Fig. 1, make  $\mathbf{Z_1}$  and  $\mathbf{Z_f}$  equal resistors R and remove all other forward impedances, then

$$\frac{\mathbf{v}_{o}}{\mathbf{v}_{1}} = -1$$

If an alteration in scale is desired the two resistors may differ

i.e.

$$\frac{V_0}{V_1} = -\frac{R_f}{R_1} = -\frac{2}{1}$$

#### (3) Summing

Referring to Fig. 1, make all impedances pure resistors.

$$Z_f$$

=  $R_f$

$Z_1$  =  $R_1$

$Z_2$  =  $R_2$

$Z_n$  =  $R_n$

Then

$$V_0 = -(V_1 \frac{R_f}{R_1} + V_2 \frac{R_f}{R_2} + \dots V_n \frac{R_f}{R_n})$$

All inputs are added in proportions depending on the respective forward path resistors.

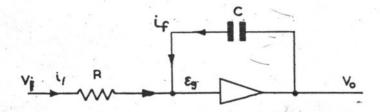

#### (4) Integrating

In this case the feedback impedance is capacitive.

$$Z_f = \frac{1}{C_p}$$

(p is the differential operator)

$$Z_1 = R$$

$Z_2$ ,  $Z_3$  etc. are removed.

Then  $\frac{V_0}{V_1} = -\frac{1}{RC_p}$  The "transfer function" representing an integration, with respect to time.

Multiple inputs can be summed and integrated in the same amplifier if  $Z_2$  =  $R_2$ ,  $Z_3$  =  $R_3$ , etc.

Alternatively: -

Fig. 2. An Integrator

Referring to Fig. 2.

Assume

$$E_g = 0$$

then,

$$i_1 = \frac{V_1}{R}$$

and  $i_f = \frac{C_d V_0}{dt}$

but,

$$i_1 + i_f = 0$$

So,

$$\frac{V_1}{R} = -\frac{C_d V_0}{dt}$$

Integrating

$$V_0 = \frac{1}{CR}$$

$\int_0^t V_1 d_t$

(5) Simple Lag

Fig. 3. Circuit for simple lag

In the circuit of Fig. 3.

$$Z_f = \frac{\frac{1}{R_f C_f p}}{\frac{1}{R_f + \frac{1}{C_f p}}} = \frac{R_f}{1 + pC_f R_f}$$

and  $Z_1 = R_1$

So

$$\frac{V_0}{V_1} = -\frac{R_f}{R_1}$$

$\frac{1}{1 + pC\epsilon R\epsilon}$

$C_f R_f$  sets the time constant of the lag and  $\frac{R_f}{R_f}$  is the scale change.

More complex transfer functions can be formed by making  $Z_f$ ,  $Z_1$ ,  $Z_2$ , etc. more complex.

N.B. There is, necessarily, a sign reversal accompanying each operation involving a D.C. amplifier.

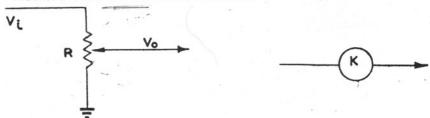

#### (6) Multiplying a Variable by a Constant k

Fig. 4(a). Coefficient potentiometer.

Fig. 4(b). Symbolic representation of coefficient potentiometer.

Neglecting the loading of the forward path impedance of the following amplifier

$$V_0 = + nV_i$$

n then represents the value of the constant k.

## (7) Dividing a Variable by a constant k

This may be accomplished with the circuit of Fig. 4(a) by calling the potentiometer  $\frac{1}{K}$ , but it is often more convenient to resort to the circuit shown below in Fig. 5.

Fig. 5(a). Coefficient potentiometer in feedback path.

Fig. 5(b). Symbolic representation.

Neglecting the loading of  $\mathbf{R}_{f}$  on the potentiometer

$$\frac{V_0}{V_1} = -\frac{1}{n} \frac{R_f}{R_1}$$

## 1.3 Setting up a problem and programming the computer

#### (1) The Flow Diagram

There are in effect two different starting points depending on the problem to be investigated.

A. When the information is given in the form of differential equations. This is so for most dynamical mechanical systems.

B. When the information is presented in the form of a system flow diagram with the transfer functions of the various paths in that diagram. The major group in this category is servo-control systems.

In case A a reasonable approach is to rewrite the equation in operational form and segregate the terms containing the highest derivative, equating this to all other terms.

If the highest derivative term is integrated a sufficient number of times to obtain the lowest, each derivative produced can be fed through suitable coefficient setting devices (and sign changes where necessary), then summed and equated to the original term (i.e. the highest derivative).

Example: - Second order with spring, mass, damping.

$$\frac{d^2}{dt^2}x + 2 \mathop{ \sum}\limits_{}^{} W_n \, \frac{dx}{dt} + W_n^2$$

.  $x = f(t)$

$\xi$  is damping ratio and  $W_n$  is undamped natural frequency and f(t) the forcing function.

Writing p for d and transposing

$$p^2x = -(2 \xi W_n p + W_n^2)x + f(t)$$

Now the flow diagram can be drawn

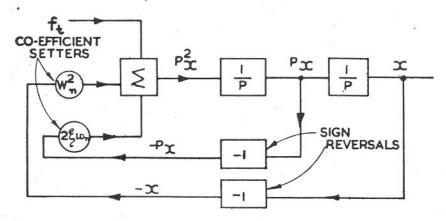

Fig. 6. Computer flow diagram for second order differential equation. The next step is to draw the computer schematic diagram.

Fig. 7. Computer schematic diagram for second order differential equation.

Note: Since each amplifier inherently reverses the sign, only one sign changing amplifier (in the damping loop) is necessary.

The coefficient setting devices are potentiometers connected as described in the sixth section under the previous heading.

When information exists in the form of a system flow diagram then the computer schematic can be drawn directly from that diagram, each transfer function being simulated in turn by suitable amplifier-passive component combinations. Sometimes re-arrangement of the existing flow diagram simplifies the computer set-up.

#### (2) The Time Scale

Before deciding upon computer component values the problem time scale must be fixed. Investigations which involve simulating part of a system in conjunction with real components from that system are necessarily conducted in a 1:1 time scale. In other words, t secs. of computer time represent t secs. of real time.

The 1:1 time scale is often suitable in applications where the whole system is simulated but there are occasions when a changed scale is much more convenient. Systems in which physical variables change very slowly (process plant, heat exchangers, nuclear setc.) may usefully be speeded up in the computer. It must, however, always be because m mind that in speeding up the computer its accuracy is decreased.

Conversely, if a very fast real problem is being investigated (electrical networks, vibration isolators etc.) the time scale must be slowed down in the interests of accuracy.

#### (3) The Amplitude Scale

Firstly it is desirable to know the maximum values which the time varying parameters are likely to reach with the conditions obtaining for the investigation. Then these maximum values are represented by voltages within the saturation voltage of a computer amplifier which is a known quantity. This maximum computer voltage (in the case of Minispace 100 V) is often referred to as "the machine unit".

The scale at a particular point in the computer (i. e. of a particular physical variable) is defined as:-

The number of units of the variable which represents one machine unit, this value of the variable being greater than, or equal to the maximum value expected of that variable during the computer run.

The maximum values at which the constants are likely to be set are generally known, so that the scales of the potentiometers are greater than or equal to this value. Then the position of the potentiometer wiper sets the coefficient at a fraction n (see Fig. 4(a)) of the scale of the pot. In other words, the 100% potentiometer reading represents a chosen number of the units of the constant (this value of the constant being greater than or equal to the maximum value required during the total computation).

Naturally the scale at one position in a computer depends on the scale at the previous position, the gain of the amplifiers, and the scale of the coefficient potentiometers between those positions.

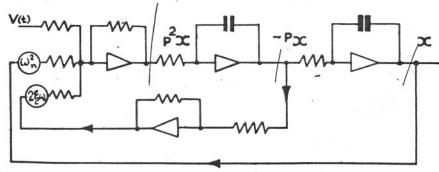

Example:- Two variables in time connected by a proportionality constant.

$\dot{y} = kx$

- (1) Maximum value of x is say 25 ins./sec.

- (2) Maximum value of k is chosen as 20 square ins.

- (3) Assume that for initial studies k will be set lower than 4 sq. ins., then maximum value of y is 100 cu. ins./sec.

Then the scale of x is 25 ins./sec. (i.e. 25 ins./sec. is represented by 1 machine unit), the scale of y is 100 cu. ins./secs. and the scale of the potentiometer is 20 sq. ins. (i.e. 100% on the pot represents 20 sq. ins.).

The following scaled computer schematic may now be drawn.

Fig. 8. Scaled computer diagram for y = kx.

To check the scaling numerically from point A to point B, take the scale at A, multiply it by the pot scale and divide by the amplifier gain. This should give the scale at B.

i. e. 25 x 20

$$\times \frac{1}{5}$$

= 100

Provided scaling is carried out using the principles defined, to obtain the scale at one point in the computer from the scale at a prior point, multiply by potentiometer scales and divide by amplifier gains in the path connecting those points.

The scale change across an integrator is determined by the time constant of that integrator. For the purposes of scaling this can be considered in precisely the same way as the gain of the scale change amplifier in the above example. If the scale at the integrator input is S units/machine unit, and the scale at the output is P units/machine unit, then P = 1 S where G = 1 RC

In complex problems the variable maximums are not always known accurately, even so an intelligent estimate can usually be made. If, subsequently, this estimate proves to be grossly inaccurate, appropriate rescaling may be implemented.

A potentiometer cannot be set to precisely the correct value on an associated dial because of the loading of the following impedance (which is changed for varying amplifier gains). In Minispace the potentiometers whilst correctly loaded are set against an adjustable reference.

The above discussion on amplitude scaling is appropriate for setting up a computer in real time. To rescale the computer for a speed up of Stimes, the integrator time constants (the RC products) must be reduced in this ratio. The inverse applies for a slow down.

#### (4) Initial Conditions

The initial condition of the equations are set up as voltages held at the appropriate integrator outputs (may be zero volts) with due regard to the scaling set at these outputs.

#### (5)Problem Check

Before continuing the problem should be checked. A recommended procedure is:-

- (1) Check connections

- (2)Check potentiometer settings

- (3)Check initial conditions

#### (6)Compute

Having arranged suitable recording equipment (C. R. O., pen recorders etc.) connected to the desired outputs, the hold condition on the integrators may be released and the computation started.

When the steady state solution has been reached, the computer can be reset, new initial conditions and coefficient values imposed and further solutions obtained.

There are, of course, problems where the forcing function is repetitive (investigating response to sine waves at various frequencies). The integrators are then held at zero until the forcing function is applied.

### 1.4 Simulating simple discontinuities

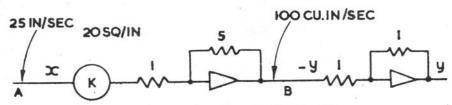

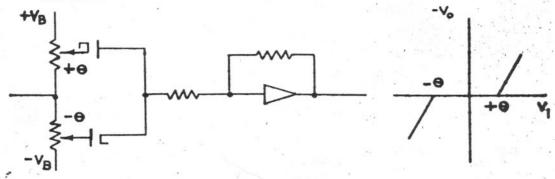

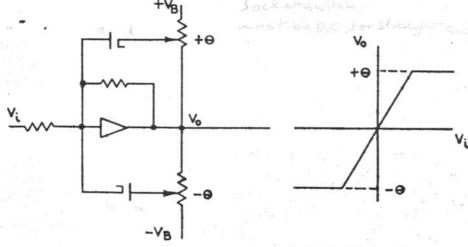

### (1) Inert Zone

Fig. 9. Circuit for inert zone - neither diode conducts until  $|v_i| > |\theta|$

## (2) Limiter

Fig. 10. Limiter circuit - an inert zone in the feedback path.

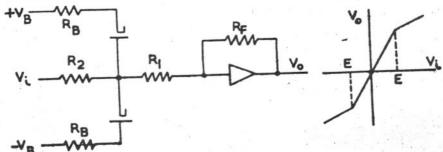

#### (3) Bi-directional 2-segment curve

Fig. 11. Two-segment curve. Slope of mid-section =  $\frac{R_F}{R_1 + R_2}$

Slope of outer section =

$$\frac{R_B R_f}{R_1 R_2 + R_B (R_1 + R_2)}$$

$$E = \frac{R_1 + R_2}{R_1} \quad V_B$$

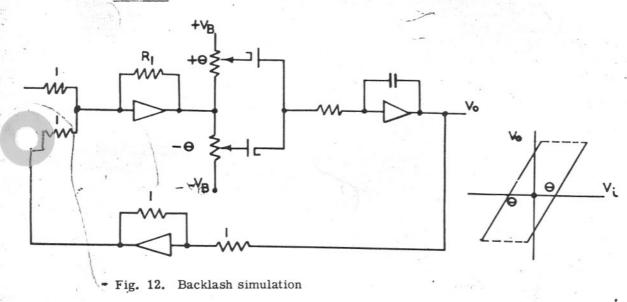

(4) Backlash

This circuit consists of an inert zone, a low time constant integrator (used as a voltage store while neither diode is conducting) and a phase reversal.

Owing to integrator drift this circuit is only suitable in problems involving rapid changes. The integrator time constant has to be made as large as possible without introducing too much phase shift between  $V_i$  and  $V_O$ .

Neglecting the inert zone

$$\frac{V_0}{V_i} = \frac{1}{1 + \frac{p}{k}}$$

where k is total forward path gain

i.e.

$$k = R_1$$

So in order to keep the dynamic phase shift small, k must be as high as possible, i.e.  $R_1$  must be large and RC small. This is, however, not compatible with small drift rate so a compromise must be reached depending on the speeds at which the variables in the problem change, and the accuracy required.

#### CHAPTER 2

#### OPERATING MINISPACE

#### 2.1 General Description of Minispace

The Minispace analogue machine is a small console equipment containing the following components.

- (1) Ten drift-corrected D.C. amplifiers type AA621.2 mounted in two racks below the sloping patching desk. See appendix for specification of amplifiers.

- (2) Two heater supply units TS722.2 for the above amplifiers, mounted in the racks with the amplifiers.

- (3) Four stabilised power supply sub-units giving  $\pm$  300 V with total current output of  $400 \, \text{mA} \pm 100 \, \text{V}$  (0.2%) 50 mA reference supplies. There is spare power of 50 mA at  $\pm$  300 V for external units which may be used in conjunction with "Minispace".

- (4) A cooling fan.

- (5) Permanently wired input and feedback components associated with each amplifier. Two 100 K $\Omega$  and two 1 M $\Omega$  (0.1% tolerance, high stability) resistors in the forward path of all amplifiers. In the "row A" amplifiers either a 1 M $\Omega$  (0.1%) resistor or a 1  $\mu$ F (0.5%) capacitor can be switched into the feedback path and in "row B" amplifiers either a 1 M $\Omega$  or a 0.1  $\mu$ F (0.5%) feedback component can be selected.

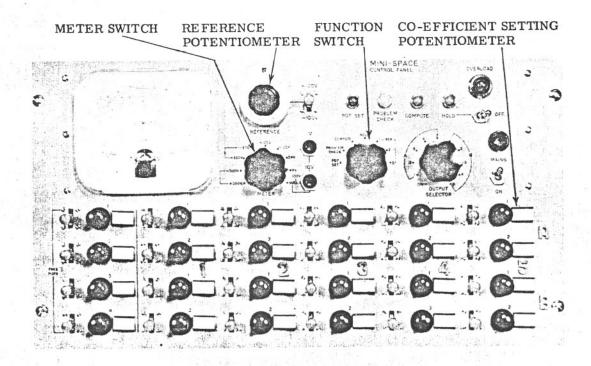

Plate 1. Control and potentiometer Panel

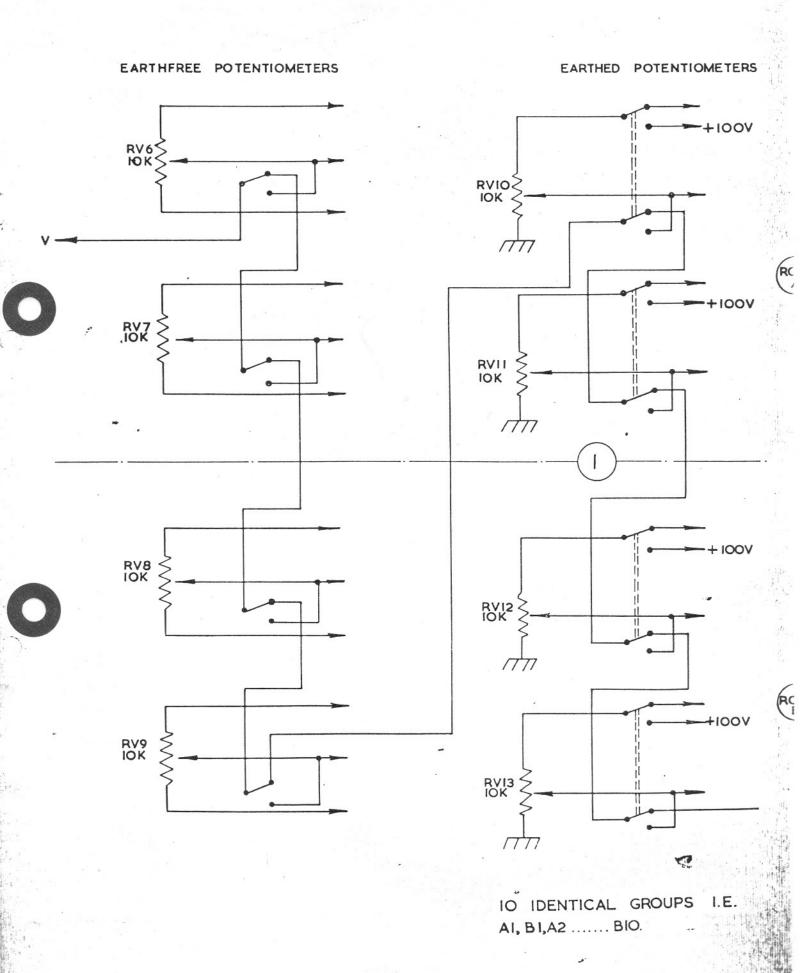

- (6) Twenty wirewound ten-turn helical potentiometers with one end permanently earthed, for coefficient and initial condition setting, attenuation etc., and four similar earth-free potentiometers all mounted on the lower half of the control panel.

- (7) Four pairs of diodes, each pair having one anode to cathode connection, to be used with the "earth free" potentiometers for the generation of discontinuous functions.

- (8) A centre-zero meter, with 3 ranges 1, 10 and 100 volts full scale, push button selected, mounted on the left hand side of the control panel.

- (9) A "Meter Switch", mounted adjacent to the meter, enabling the various supply and reference voltages to be monitored.

- (10) A direct reading ten-turn helical potentiometer (0.1% linearity) to be used in conjunction with the reference supply and the centre zero meter, to set coefficients and initial condition potentiometers.

- (11) A computer "Function Switch" which controls internal relays to give the following computer conditions; Potentiometer Set, Problem Check, Compute, Hold, and Repetitive. Coloured lights on the control panel indicate the selected condition.

- NOTE: Circuit diagram demonstrates clearly the automatically selected internal connections for each position of the function switch.

- (12) An eleven-position "Output Selector Switch", used to monitor any of the ten amplifier outputs on the meter, and in the "OFF" position, the coefficient potentiometer outputs (via the associated key switches) or signals applied to the "V" socket on the patch panel.

- (13) A central overload indicator which lights when any amplifier overloads. Immediately below the overload indicator is a switch which may be used in conjunction with it. This switch will "hold" the computer in the overload condition when the individual amplifier overload neons may be inspected to discover which is the offending unit.

- All items 6 13 inclusive are mounted on the control panel.

- (14) A patching panel mounted on the sloping desk below the central panel. Multicoloured 3 mm sockets are used throughout to which amplifier, potentiometer, computing element and diode connections are made. A complete description of the patch panel is given in the section headed "Patching".

- (15) A multiway socket (on a sub-panel on the back of the equipment) to which all connections are made to enable two Minispace computers to be coupled together and operated as a single unit from one of the control panels.

- (16) Five coax sockets (on the same sub-panel as the multiway plug), four being outputs to recording equipments, the fifth providing a trigger pulse signal for synchronising external equipment (e.g. an oscilloscope).

#### 2.2 Setting up procedure

- (1) Switch output Selector Switch to OFF, overload hold switch to OFF and Function Switch to POT SET.

- (2) Check all mains selector panels, including the fan input voltage on the auto-transformer, (to ensure that this corresponds with local mains supply) and connect up to the mains. Switch on and allow several minutes as a warming up period.

- (3) Check the 300 volt power supplies using the control panel meter. There are positions on the meter switch which enable each of the 4 power supply unit outputs to be separately monitored. (If these are not within 2% of nominal they may be adjusted in turn by potentiometers on the power units).

- (4) Check the 24 V supply and the  $\pm$  100 V reference supply, again on the meter switch. The 24 V supply should be within  $\pm$  2 V and the reference supplies can be adjusted by potentiometers RV1 and RV2 on the chassis at the back of the control panel (rear accessibility).

- (5) To zero the amplifiers AA621.2 press the balance indicator button. If the new strikes adjust the balance potentiometer until the lamp is extinguished. Hold the button in for a few moments to check that the neon does not restrike. Each amplifier has its own neon indicator and balance controls on its own individual panel.

- (6) Switch all amplifiers to sum, and Function Switch to Problem Check, Compute, Hold and the three Repetitive positions in turn, noting that the appropriate lamp is illuminated. Repeat with all amplifiers switched to INT.

Monitor all outputs under all the above conditions with the Output Selector Switch and with the Meter Switch on position V. All output voltages should be zero.

#### Patching Minispace

(1) General Description of Patch Panel

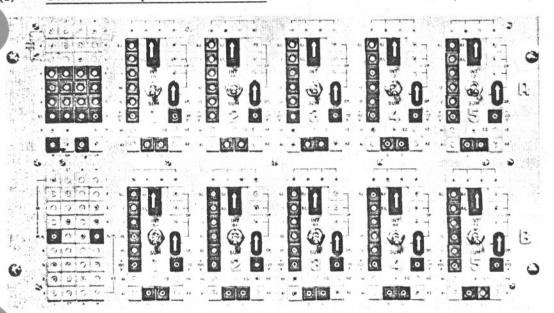

Plate 2. The Patch Panel

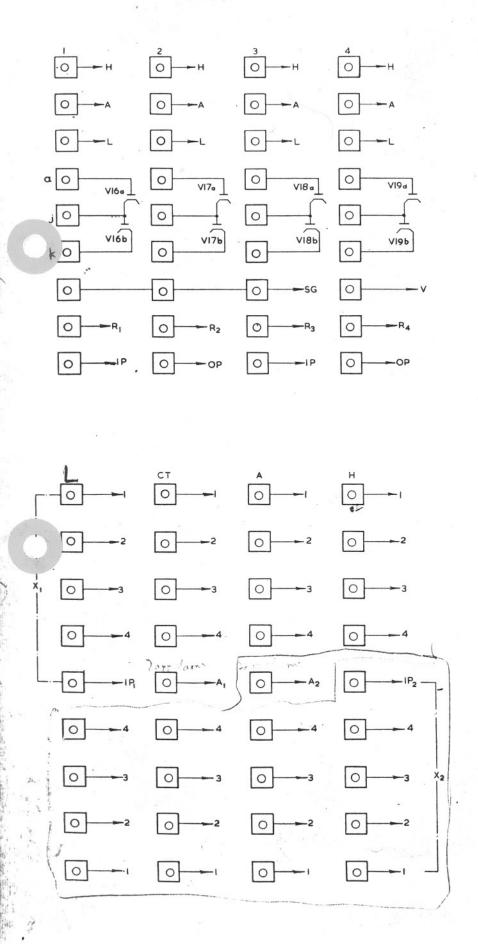

On the patch panel there are ten similar groups of 25 multicoloured 3 mm sockets, marked A, 1 to 5 and B, 1 to 5, and two unique groups of 36 sockets each.

Each group of 25 is associated with the computing elements for a particular amplifier.

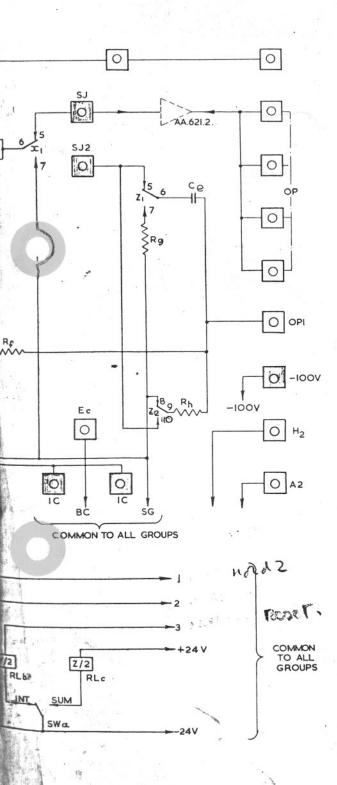

The following is a list of the connections to the sockets of a 25 way group. These can be seen in Circuit Diagram included in this handbook.

- 1. The 4 white inter-connected sockets at the top of each group are for use as a spare multiple link.

- 2. SJ1 (green) is the junction of the internal summing resistors.

- 3. The two "1" sockets (blue) are inputs to the two 1 M $\Omega$  summing resistors, i.e. unity gain inputs.

- 4. The two "10" sockets (blue) are inputs to the two 100 K $\Omega$  summing resistors, i.e. ten gain inputs.

- 5. SJ (green top centre) is the amplifier input.

- 6. SJ2 (green immediately below SJ) is the amplifier input end of the internal feedback element.

- 7. OP (4 linked yellow sockets) is the amplifier output.

- 8. OP1 (yellow) is the output end of the internal feedback element.

- 9. . ± 100 V (red & purple) are reference supplies.

- 10. H1, H2 (orange) and A1, A2 (orange) are the "high" ends and armatures respectively, of the potentiometers associated with the group.

- 11. IC (two red commoned sockets) is the input for the initial condition voltage.

- 12. EC(white). Each EC is connected to a pin on the multiway external connection socket (see circuit diagram), enabling connection to be made from any amplifier to associated apparatus without the embarrassment of long "flying" leads.

The top 36 way group is connected to the free pots, the diode pairs, signal ground, the voltmeter, recording outputs and the multiway terminations for external control functions.

The connections are as follows:-

- 1. Rows H, A, L by columns 1, 2, 3, 4 (all orange) are "high" end, "armature" and "low" end connections to free pots.

- 2. Rows a, (blue), j, (green), k, (red), are adequately explained in Circuit Diagram.

- Three black sockets marked SG are signal ground.

- The purple socket V in the same row as SG is the meter input.

- 5. R1, R2, R3, R4 (white) are connected to the coax output recorder sockets on the back of the equipment.

- 6. The two pairs of IP, OP, socket (blue and yellow respectively) are connected to the multiway external connection socket. They are intended as extra input/output connections to associated equipment.

The lower 36 way group is the patch panel for the two servo-multipliers which may be included to expand the facilities of the machine.

In addition there are two groups of sockets on the narrow penal between the control and patch panels. The first group has six sockets connected to the contacts of the adjacent double pole changeover switch. The second group has eight sockets connected to the coil and double pole changeover contacts of a relay. Thus single or double pole, on-off or changeover operations may be patched for manual or remote operation.

#### (2) Patching Specific Operations

Transfer functions are connected using the patch cords and two-pin link plugs provided and the integrate/sum switches.

The following operations are patched using the internal computing components. For all operations using the internal feedback elements two-pin links should be used to connect SJ to SJ2 and OP1 to the lowest OP socket.

#### (a) Summing

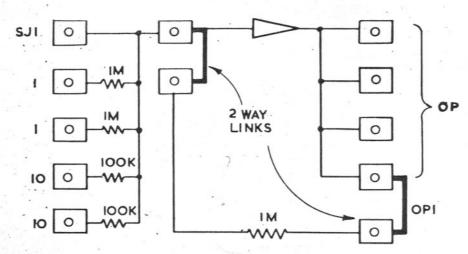

The switch associated with the amplifier patching group should be switched to SUM. Internal relays then make the circuit shown in Fig. 13 available; a summer with 2 unity gain and 2 ten times inputs. This circuit is open to variation. For instance a patch cord might be used to connect an OP socket to a "1" input. There are then two 1 M $\Omega$  resistors in parallel in the feedback path giving two inputs gain 5 and one gain 0.5.

Fig. 13. Summing circuit.

#### (b) Integrator

. The switch associated with the amplifier patch group must be switched to  ${\tt INT.}$

The circuit available is then as in Fig. 13 but the 1 M $\Omega$  feedback resistor becomes a 1.0  $\mu$ F capacitor for A row amplifiers and a 0.1  $\mu$ F for B row amplifiers. Thus for A row amplifiers there are two integrator inputs at 1 sec. time constant and two at 0.1 secs. and for B row two at 0.1 secs. and two at 0.01 secs.

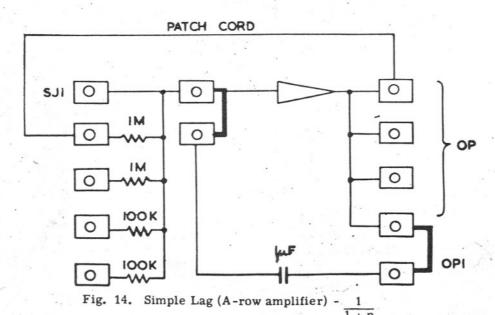

#### (c) Simple Lag 1/(1 + pT)

The sum/integrate switch must be at INT. Connect an OP socket to either a "1" or "10" input socket with a patch cord. Then the chosen forward path resistor in fact becomes a feedback resistor in parallel with either a 1  $\mu F$  or 0.1  $\mu F$  capacitor as shown in Fig. 14.

With the circuit patched as shown

$$\frac{V_0}{V_i} = -\frac{1}{1+r}$$

If the patch cord linked OP with a "10" input socket

$$\frac{V_{O}}{V_{i}} = -\frac{1}{10} \frac{1}{1 + p/10}$$

Other combinations can be obtained as desired. For example, two input resistors could be paralleled into the feedback path, perhaps using the spare 4-way multiple as further amplifier output sockets if required, merely by linking it to an OP socket. In this way either 500 K $\Omega$  or 50 K $\Omega$ , say, could be put in parallel with the feedback capacitor and at the same time several amplifier output sockets would still be available.

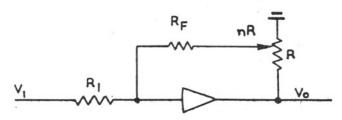

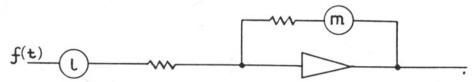

#### (d) Multiplying and Dividing by a Constant

Potentiometers are used specifically for this purpose (i.e. as coefficient setting devices) but they are also very useful as simple attenuators or to give non-integral values of amplifier gain or integrator time constant. They are similarly patched in any employment.

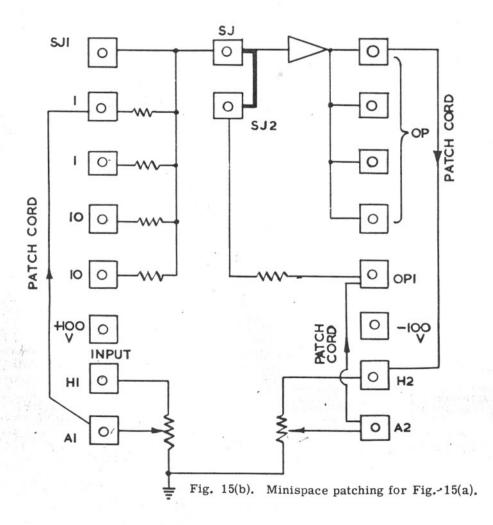

An example of multiplying one constant "1" and dividing by another "m" is shown in Fig. 15 to illustrate the method of patching potentiometers.

Fig. 15(a). Multiplying a variable f(t) by "1" and dividing by "m".

N. B. There is no 2-way link from OP1 to OP.

#### (e) Example

Description of patching the equation y = kx from CHAPTER 1, Section 1.3(3), scaled as in that section.

Use amplifier "A1" as a scale change and "A2" as a sign reversal, and potentiometer "A1" for the coefficient k.

- (1) For both amplifiers the sum/integrate switch is set at SUM, and connections SJ to SJ2 and OP1 to OP are made.

- (2) Input signal x goes into the "high" end H1 of potentiometer "A1". The armature socket A1 of this pot is patched to one of the 10 gain inputs of "A1" amplifier.

- (3) Patch from an OP socket of "A1" amplifier to one of its own input sockets. This amplifier then has the correct gain of 5.

- (4) Another patch cord connects a further "A1" amplifier OP socket to a "1" input of "A2" amplifier.

- (5) The output y then comes from OP of "A2" amplifier.

Setting the coefficient potentiometer is described under the first heading of the next section "Computer Functions".

### (f) More Complex Transfers

With a little ingenuity more complex transfer functions can be patched using the internal components. Also, if the links SJ to SJ2 and OP1 to OP are not made, complex filters can be used as the feedback impedances of the amplifiers. External forward path elements can be patched into SJ1 as required.

#### 2.4 Computer Functions

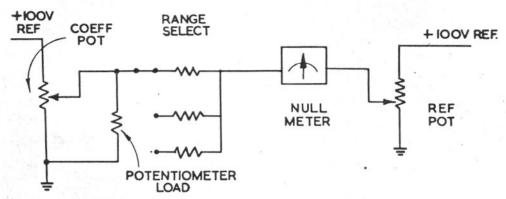

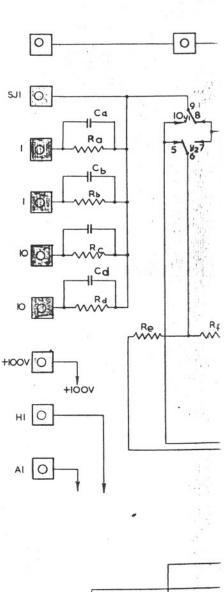

#### (1) Setting Coefficient Potentiometers

- (a) Turn the Meter Switch to NULL and the Function Switch to POT SET. This latter earths the summing junction of the forward path components. All coefficient potentiometers are then correctly loaded by their respective amplifier forward path resistors earthed at the summing junction end.

- (b) Set the reference potentiometer on the control panel to the required coefficient value.

- (c) Connect the +100 V reference to the 'high' end of the reference potentiometer by means of the associated key switch.

- (d) Depress the key switch associated with the specific coefficient pot. This disconnects the "high" end of the potentiometer from the H patch socket and connects it to the +100 V reference, and simultaneously connects the potentiometer armature (wiper) to the meter through the sensitivity changing network.

- (e) Adjust the coefficient potentiometer until balance is indicated on the meter.

- (f) Repeat (e) with the 10 V range selected on the appropriate push button.

- (g) Repeat (e) with the 1 V range selected. When a null has been attained zero current flows into the meter, so the reference potentiometer is not loaded and the coefficient potentiometer has only its correct load (i.e. of the amplifier input impedance).

Fig. 16. Circuit for setting coefficient potentiometer.

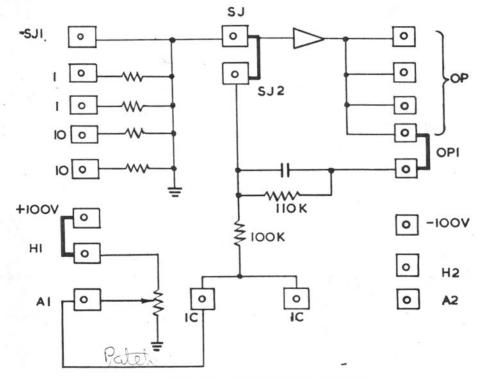

## (2) Setting Initial Conditions

(a) Turn the Meter Switch to NULL and the Function Switch to POT SET. All amplifiers switched to integrate hen have extra forward path and feedback resistors introduced as shown in Fig. 17.

Fig. 17. Setting Initial Conditions.

- (b) Link the "high" end of the initial condition potentiometer to the 100 V reference (select the correct polarity remembering that there is a sign reversal in the amplifier). Then patch the armature of that potentiometer to one of the 1C sockets.

- (c) Monitor the voltage at the integrator output by turning the Selector Switch to the appropriate position.

- (d) Set up the initial condition on the reference potentiometer.

- (e) Using the associated key switch connect either the positive or negative  $100\ V$  reference to the reference potentiometer. The polarity must correspond with that of the initial condition.

(f) Adjust the reference pot until a null is obtained, exactly as for coefficient setting. The initial condition resistors are 2% tolerance. The ratio of 1.1 to 1 chosen between the feedback and forward paths thus allows all voltages from 0 - 100 to be easily obtained at the integrator output even under the worst tolerance conditions.

#### (3) Problem Check

- (a) Turn the Function Switch to the PROBLEM CHECK position. All integrators are then in the same condition as for POT SET. All summing amplifiers are connected as they would be for computing.

- (b) Scan the integrator outputs on the meter with the Selector Switch, the Meter Switch being turned to position V. This checks the initial conditions as a direct voltmeter reading.

- (c) The procedure of Coefficient Setting can be repeated as a check.

All summing amplifier outputs may be monitored using the Selector Switch. These voltages will be dependent on the initial conditions on the first previous integrators, the correct amplitude and polarity being easily determined from inspection of the computer schematic diagram.

#### (4) Computer

When COMPUTE is selected on the Function Switch internal relays automatically release the integrators (i.e. remove the initial condition resistors) and simultaneously reconnect the summing junctions to the integrator amplifier inputs. The circuit is then exactly as the computer schematic.

#### (5) Hold

The Function Switch may be turned to HOLD at any desired time after computing has started.

This disconnects the summing junctions of the forward path elements from the integrator amplifier inputs and earths them. This leaves the feedback capacitor charged at the precise voltage when computing is arrested. The problem can be frozen at any time t after the commencement of the compute period and the solution at this time recorded at leisure on D.C. recording devices (see appendix).

#### (6) Repetitive

There are three repetitive positions on the Function Switch, automatically switching the computer between the COMPUTE and PROBLEM CHECK (called 'RESET' for this purpose) conditions.

Position 1 1 sec. compute period 1 sec. reset

Position 2 2 sec. compute period 1 sec. reset

Position 5 5 sec. compute period 1 sec. reset

#### (7) Accurate Measurement of D. C. Voltages

The null method may be used to measure accurately unknown D.C. voltages. The Meter Switch should be turned to NULL, the voltage patched to the V socket on the upper 36 way patch group, the reference supply of the appropriate polarity applied to the reference potentiometer, and the reference potentiometer adjusted to attain meter balance. Then the measured value is obtained as a dial reading on the potentiometer.

#### APPENDICES

#### Appendix 1.

#### Specification of D.C. amplifier AA 621.2

DC Amplifier AA621.2: DC Gain:  $>30 \times 10^6$ ; at 100 c/s  $>10 \times 10^3$ .

Drift:  $\langle 100\mu V \text{ (Long Term)} \rangle$  Referred to Typically  $20\mu V$  per day Noise: Typically  $100\mu V$  Summing Unity Integrator Drift:  $(1\mu F \text{ and } 1M\Omega) < 100\mu V/\text{sec.}$  Bandwidth (3db):  $16 \text{ Ke/s at} \times 10 \text{ gain.}$

$(1M\Omega \text{ Feedback}): 9 \text{ Kc/s at } \times 100 \text{ gain.}$

Typical safe capacitance loading with a 1M Ω feedback resistor 10,000 pF at output with 250 pF at summing

junction.  $20k\Omega$  or  $10k\Omega$ . Output :  $> \pm 100$ V into :

) + 300V at 20mA or 31mA HT Consumption Max : At  $\pm 100 \text{V o/p}$   $\int -300 \text{V}$  at 19mA or 25mA

#### Appendix 2.

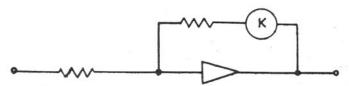

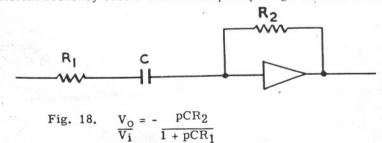

#### The Differentiating Circuit

In theory a differentiating circuit is easily obtained. A computing amplifier with a capacitor in the forward path and a resistor in the feedback path gives the transfer function.

$$\frac{V_O}{V_i}$$

= - pCR (p being  $\frac{d}{dt}$ )

However, such a circuit has the following disadvantages which preclude its use.

- The gain increases with frequency, at a rate of 6 db/octave, so spurious high frequency voltages which appear at the input (due to pick up, thermal noise in resistors etc.) are greatly amplified, perhaps to such an extent that the signal may be swamped.

- The feedback amplifier stability margin is greatly decreased.

Flow diagrams which seem to demand the use of differentiators can often be re-arranged to exclude them. If this is inherently prohibited the differentiation may possibly be accomplished with sufficient accuracy over a limited frequency range with the circuit shown in Fig. 18.

For frequencies at which pCR $_1 << 1$

$\frac{V_{O}}{V_{i}}$  = - pCR<sub>2</sub>, and the circuit behaves as a differentiator.

When pCR<sub>1</sub> >> 1

$$\frac{V_0}{V_i} = -\frac{R_2}{R_1}$$

Thus the gain/frequency response characteristic flattens out at the high frequency end.

Appendix 3.

#### Computer Limitations

## To show that the accuracy of computation depends on the amplifier open loop gain.

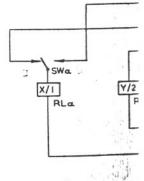

Firstly, to define the amplifier open loop gain YL consider the circuit of Fig. 19.

Fig. 19. Generalised computer amplifier in open loop condition.

The forward path gain is

$$\frac{V_O}{E_g} = - \propto$$

(1)

The feedback path gain (with input earthed) is

$$\frac{E_S}{V_O} = \frac{Z_i}{Z_i + Z_{fb}}$$

(2)

So the total gain  $Y_L$  around the amplifier loop when the switch at the summing node is closed is given by

$$Y_{L} = \underbrace{E_{S}}_{E_{g}} = -\underbrace{\alpha Z_{i}}_{Z_{fb} + Z_{i}}$$

(3)

Now with the loop closed (i.e. switch S closed)

$$V_0\left(\frac{1}{Z_{fb}} + \frac{1}{\infty} \cdot \left(\frac{1}{Z_{fb}} + \frac{1}{Z_i}\right)\right) = -\frac{V_i}{Z_i}$$

(see section 1.2(1) Chapter 1)

which may be written

$$\frac{V_O}{V_i} = -\frac{Z_{fb}}{Z_i} \left( \frac{1}{1 + \frac{Z_i + Z_{fb}}{\alpha Z_i}} \right) \tag{4}$$

i.e.

$$\frac{V_0}{V_i} = -\frac{Z_{fb}}{Z_i} \frac{(\frac{1}{1-1})}{(\frac{1}{YL})}$$

(5

Thus Y<sub>L</sub> must be very high in order that  $\frac{V_O}{V_i}$  = -  $\frac{Z_{fb}}{Z_i}$

For a summing amplifier  $Z_i$  represents all the forward path resistors in parallel. So, depending on the computation accuracy required and the various values of the computing elements, the number of inputs is limited. Considering a specific case; assume that the required accuracy is 0.1% at 100 c/s (neglecting the tolerances on the computing passive elements).

YL must be greater than 103

So.

$$\frac{Z_i}{Z_i + Z_{fb}} \leqslant \frac{1}{10}$$

Then (a) for a summing amplifier with all computing components 1 M  $\Omega$ , the maximum number of inputs is 9.

(b) for a scale change amplifier with one input the maximum gain allowable is say 10 (strictly speaking 9).

Similar figures may be obtained for integration remembering that the feedback element in this case is frequency dependent.

Since the amplifier gain ' $\propto$ ' decreases with increasing frequency (20 db. per decade) so the loop gain also decreases.

The accuracy required for each individual problem of course, varies, but in general it is not recommended that the computer is used above a frequency of 500 c/s.

(A further limitation on the frequency of operation is the fact that the power output from the amplifiers decreases with frequency so a voltage swing of less than the nominal  $\pm$  100 is available from a loaded amplifier).

#### Amplifier saturation

At D. C. the amplifiers will give  $\pm$  100 V output into 10 KO. For nett load impedances less than this the voltage swing available is less than 100.

#### 3. The limit on computer "hold" time

When the "hold" facility is used the voltages on the integrators do not persist indefinitely at the arrested values because of small grid and leakage currents at the amplifier input. The percentage accuracy of the reading depends on the size of the integrator capacitor, the amplitude of the "stored" voltage, the input current and the "hold" time.

The rate of change of voltage,  $\frac{dV}{dt}$ , for an input current  $i_g$  is given by

$$\frac{dV}{dt} = \frac{i_g}{C}$$

If  $i_g = 10^{-10}$  amps,  $C = 0.1 \mu F$ , then

$$\frac{dV}{dt} = \frac{10^{-10}}{10^{-7}} = 10^{-3} \text{ volts/second}$$

Assume the nominal voltage to be measured is 10 volts. After 10 secs. the accuracy of the measurement would be 0.1%.

The drift current of the Minispace Amplifier is approximately 5. 10-11 A at the input terminal.

Fig. 20. Mir

|             |    | GROUP | LAYOUT |      |    |

|-------------|----|-------|--------|------|----|

| SHOWN       | AI | A2    | А3     | . A4 | A5 |

| AS<br>SHOWN | ВІ | B2    | В3     | B4   | B5 |

|                      | Lines     | Relay Contacts Closed |     |     |     |      |      |      |     |      |     |

|----------------------|-----------|-----------------------|-----|-----|-----|------|------|------|-----|------|-----|

| Condition            |           | Sum                   |     |     |     |      | Int, |      |     |      | -   |

|                      | Energised | X1                    | Y1  | Y2  | Z1  | Z2   | X1   | Y1   | Y2  | Z1   | Z2  |

| Pot Set              | 1 & 3     | 6-7                   | 9-8 | 6-5 | 6-7 | 9-10 | 6-5  | 9-10 | 6-7 | 6-5  | 9-8 |

| Problem Check        | 3         | 6-5                   | 9-8 | 6-5 | 6-7 | 9-10 | 6-5  | 9-10 | 6-7 | 6-5  | 9-8 |

| Compute              | None      | 6-5                   | 9-8 | 6-5 | 6-7 | 9-10 | 6-5  | 9-8  | 6-5 | 6-5  | 9-8 |

| Hold                 | 2         | 6-5                   | 9-8 | 6-5 | 6-7 | 9-10 | 6-7  | 9-8  | 6-5 | 6-5" | 9-8 |

| Repetitive (Reset)   | 3         | 6-5                   | 9-8 | 6-5 | 6-7 | 9-10 | 6-5  | 9-10 | 6-7 | 6-5  | 9-8 |

| Repetitive (Compute) | None      | 6-5                   | 9-8 | 6-5 | 6-7 | 9-10 | 6-5  | 9-8  | 6-5 | 6-5  | 9-8 |

inispace Patch Panel

Fig. 21. Coefficient setting potentiometers